#### FW-7911

Network Security Barebone

User's Manual V1.1

# 用户手册 USER'Manual

#### FW-7911

Network Security Barebone

User's Manual V1.1

Shenzhen NORCO Intelligent Technology Co., Ltd.:0755-27331166

Beijing: 010-82671166

Shanghai: 021-61212088

Nanjing: 025-58015489

Chengdu: 028-85259319

Shenyang: 024-23960846

Xi'an: 029-88338386

Nanjing: 025-58015489

Wuhan: 027-87858983

Tianjin: 022-23727100

Netherlands: 31- (0) 40-2028140

Germany: +49 40 7003550

Austria: 4316150499-88

Website: <a href="www.norco-group.com">www.norco-group.com</a>

# Declaration of conformity

#### Shenzhen NORCO Intelligent Technology Co.,Ltd.

declares that the product

#### FW-7911 Network Security Barebone

(reference to the specification under which conformity is declared in accordance with 89/336 EEC-EMC Directive)

☑ EN 55022 Limits and methods of measurements of radio disturbance

Characteristics of information technology equipment

☑ EN 50081-1 Generic emission standard Part 1:

Residential, commercial and light industry

☑ EN 50082-1 Generic immunity standard Part 1:

Ressidential, commercial and light industry

#### **European Representative:**

Shenzhen NORCO Intelligent Technology Co.,Ltd.

Signature: \_\_\_\_\_\_ Place/Data: HONG KONG/2007

Printed Name: Anders Cheung Position/Title: President

# Declaration of conformity

Trade Name: Shenzhen NORCO Intelligent Technology Co.,Ltd.

Model Name: FW-7911

Responsible Party: Shenzhen NORCO Intelligent Technology Co., Ltd.

Equipment Classification: FCC Class B Subassembly

Type of Product: Network Security Barebone

Manufacturer: Shenzhen NORCO Intelligent Technology Co.,Ltd.

#### Supplementary Information:

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Signature: \_\_\_\_\_

Date: 2008

#### Content

| Chapter 1 Product Introduction                 | 1  |

|------------------------------------------------|----|

| 1.1 Overview                                   | 1  |

| 1.2 H/W Specification                          | 1  |

| Chapter 2 Installation Instruction             | 3  |

| 2.1 FW-7911 Structure View                     | 3  |

| 2.2 Outline Dimension                          | 3  |

| 2.3 Install CPU and DIMM                       | 4  |

| 2.3.1 Install CPU                              | 5  |

| 2.3.2 Install UDDIMM                           | 5  |

| 2.4 Jumper Setting                             | 5  |

| 2.4.1 CMOS Clearance/Hold Jumper Setting (JCC) | 5  |

| 2.4.2 WDOG Setup                               | 6  |

| 2.4.3 AFC-542E V1.2 Pins (J1, J2)              | 7  |

| 2.5 Interface Description                      | 7  |

| 2.5.1 SATA and SATA Power Connector            | 7  |

| 2.5.2 CF Card Socket (Compact Flash)           | 9  |

| 2.5.3 USB(USB23, USB45, 2x standard USB)       | 9  |

| 2.5.4 Serial Ports                             | 10 |

| 2.5.5 Parallel Ports(LPT)                      | 11 |

| 2.5.6 LPC (JLPC)                               | 12 |

| 2.5.7 GPIO (JGP)                               | 13 |

| 2.5.8 Keyboard and Mouse Connector (KM)        | 14 |

| 2.5.9 MINI_PCIE (MINI_PCIE, J_LLED)            | 14 |

| 2.5.10 FAN Connector(CPUFAN1, SYSFAN1-3)       | 15 |

| 2.5.11 Power Interface (ATX, PWR)              | 16 |

| 2.5.12 Front Panel Connector (JFP)             | 17 |

| 2.5.13 PCI Expansion Slot                      | 17 |

| 2.5.14 PCIE Expansion Slot                     | 18 |

| 2.6 Network Module Description                 | 18 |

| 2.6.1 AFC-551E                                 | 18 |

| 2.6.2 AFC-541E                                 | 19 |

| 2.6.3 AFC-542E       19         2.6.4 AFC-542E-2x RJ45 LAN Port       20         Chapter 3 BIOS Setup       22         AMI BIOS Upgrading       22         AMI BIOS Description       22         BIOS Parameter Configuration       23         3.1 Main Menu       23         3.2 Advanced Menu       24         3.2.1 CPU Configuration       25         3.2.2 IDE Configuration       27         3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix       43         Appendix       45 |                                          |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----|

| Chapter 3 BIOS Setup       22         AMI BIOS Upgrading       22         AMI BIOS Description       22         BIOS Parameter Configuration       23         3.1 Main Menu       23         3.2 Advanced Menu       24         3.2.1 CPU Configuration       25         3.2.2 IDE Configuration       27         3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.7 USB Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix       43                                                                                   | 2.6.3 AFC-542E                           | 19 |

| AMI BIOS Upgrading       22         AMI BIOS Description       22         BIOS Parameter Configuration       23         3.1 Main Menu       23         3.2 Advanced Menu       24         3.2.1 CPU Configuration       25         3.2.2 IDE Configuration       27         3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.7 USB Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix       43                                                                                                                                                           | 2.6.4 AFC-542E-2x RJ45 LAN Port          | 20 |

| AMI BIOS Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Chapter 3 BIOS Setup                     | 22 |

| BIOS Parameter Configuration       23         3.1 Main Menu       23         3.2 Advanced Menu       24         3.2.1 CPU Configuration       25         3.2.2 IDE Configuration       27         3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       30         3.2.5 APM Configuration       30         3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                           | AMI BIOS Upgrading                       | 22 |

| 3.1 Main Menu       23         3.2 Advanced Menu       24         3.2.1 CPU Configuration       25         3.2.2 IDE Configuration       27         3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.7 USB Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix I: Watchdog Programming Guide       43                                                                                                                                                                                                                   | AMI BIOS Description                     | 22 |

| 3.2 Advanced Menu       24         3.2.1 CPU Configuration       25         3.2.2 IDE Configuration       27         3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix       43                                                                                                                                                                                                                                                                      | BIOS Parameter Configuration             | 23 |

| 3.2.1 CPU Configuration       25         3.2.2 IDE Configuration       27         3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix       43                                                                                                                                                                                                                                                                                                         | 3.1 Main Menu                            | 23 |

| 3.2.2 IDE Configuration       27         3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                    | 3.2 Advanced Menu                        | 24 |

| 3.2.3 SuperIO Configuration       28         3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix       43         Appendix       43                                                                                                                                                                                                                                                                                                                                                                 | 3.2.1 CPU Configuration                  | 25 |

| 3.2.4 AHCI Configuration       29         3.2.5 APM Configuration       30         3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.2.2 IDE Configuration                  | 27 |

| 3.2.5 APM Configuration       30         3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.2.3 SuperIO Configuration              | 28 |

| 3.2.6 Remote Access Configuration       30         3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.2.4 AHCI Configuration                 | 29 |

| 3.2.7 USB Configuration       32         3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.5 APM Configuration                  | 30 |

| 3.3 PCI PnP Menu       33         3.4 Boot Menu       34         3.4.1 Boot Settings Configuration       35         3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.2.6 Remote Access Configuration        | 30 |

| 3.4 Boot Menu       .34         3.4.1 Boot Settings Configuration       .35         3.4.2 Boot Device Priority       .36         3.4.3 Hard Disk Drives       .37         3.5 Security Menu       .38         3.6 Chipset Menu       .38         3.6.1 North Bridge Configuration       .40         3.6.2 South Bridge Chipset Configuration       .41         3.7 Exit Menu       .42         Appendix       .43         Appendix 1: Watchdog Programming Guide       .43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.7 USB Configuration                  | 32 |

| 3.4.1 Boot Settings Configuration       .35         3.4.2 Boot Device Priority       .36         3.4.3 Hard Disk Drives       .37         3.5 Security Menu       .38         3.6 Chipset Menu       .38         3.6.1 North Bridge Configuration       .40         3.6.2 South Bridge Chipset Configuration       .41         3.7 Exit Menu       .42         Appendix       .43         Appendix 1: Watchdog Programming Guide       .43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3 PCI PnP Menu                         | 33 |

| 3.4.2 Boot Device Priority       36         3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.4 Boot Menu                            | 34 |

| 3.4.3 Hard Disk Drives       37         3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.4.1 Boot Settings Configuration        | 35 |

| 3.5 Security Menu       38         3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.4.2 Boot Device Priority               | 36 |

| 3.6 Chipset Menu       38         3.6.1 North Bridge Configuration       40         3.6.2 South Bridge Chipset Configuration       41         3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.4.3 Hard Disk Drives                   | 37 |

| 3.6.1 North Bridge Configuration       .40         3.6.2 South Bridge Chipset Configuration       .41         3.7 Exit Menu       .42         Appendix       .43         Appendix 1: Watchdog Programming Guide       .43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.5 Security Menu                        | 38 |

| 3.6.2 South Bridge Chipset Configuration       .41         3.7 Exit Menu       .42         Appendix       .43         Appendix 1: Watchdog Programming Guide       .43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.6 Chipset Menu                         | 38 |

| 3.7 Exit Menu       42         Appendix       43         Appendix 1: Watchdog Programming Guide       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.6.1 North Bridge Configuration         | 40 |

| Appendix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.6.2 South Bridge Chipset Configuration | 41 |

| Appendix 1: Watchdog Programming Guide43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.7 Exit Menu                            | 42 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Appendix                                 | 43 |

| Appendix 2: Glossary45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Appendix 1: Watchdog Programming Guide   | 43 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Appendix 2: Glossary                     | 45 |

# MORCO

# **Chapter 1 Product Introduction**

## **Chapter 1 Product Introduction**

#### 1.1 Overview

FW-7911 is a low power Xeon based network security barebone with 10x Gigabit Ethernet ports. 2U, rackmountable, 1.2mm hihg-intensity fine carbon steel chassis. System adopts Intel 3420 PCH single chip and supports Intel Lynnfield X3450 CPU (compatible with X3400 series). 4x dual channel DDR3 UDIMM with ECC function. As for storage, system provides 2 SATA ports and one CF card socket; The Intel 3420 PCH inside supports RAIDO. 1. 5. 10, 10x GbEs and various photoelectric devices. With high-grade 2U industrial specialized power supply and exclusive "watchdog"+ BYPASS function, FW-7911 is very suitable for various network security devices, firewalls, intrusion detection systems, intelligent terminals based on tele-communications network or computer network and so on.

#### 1.2 H/W Specification

| 1.2 1/W Opcomodition |                      |                                                     |

|----------------------|----------------------|-----------------------------------------------------|

| Motherboard          |                      | FWMB-7911 V1.1                                      |

| Network Card 1       |                      | AFC-551E V1.0                                       |

| Network Card         | 12                   | AFC-541E V1.2                                       |

| Network Card         | 13                   | AFC-542E V1.2                                       |

|                      | Display<br>Interface | VGA                                                 |

| Display              | Chip                 | SM750                                               |

|                      | Video Memory         | 16MB                                                |

| Ctorogo              | SSD                  | 1x CF                                               |

| Storage              | HDD                  | 2x SATA II                                          |

|                      | PS/2                 | Inbuilt 1 set standard Pin                          |

|                      | СОМ                  | 1x RJ45 (front panel), inbuilt one set standard pin |

| I/O                  | USB                  | 2x USB2.0 (front panel), inbuilt 4 x USB2.0 pin     |

|                      | LPT                  | 1x LPT Pin (inbuilt)                                |

|                      | LPC                  | 1 x LPC Pin(Inbuilt)                                |

| Ethernet             | SFP                  | 4x SFP ( optional 8, 4, 0)                          |

| Ememer               | RJ45                 | 4x RJ45 ( optional 8, 4, 0)                         |

| Chipset              |                      | Intel 3420 PCH single chip                          |

# **Network Security Barebone**

| Memory                     | 4x DDR3 UDIMM, dual channel , ECC memory supported |

|----------------------------|----------------------------------------------------|

| System Button              | 1x Auto Reset Button                               |

| LED Indicator              | 1x PWR LED, 1x HDD LED                             |

| Power Supply               | 2U power supply ≥ 350W recommended                 |

| Cooling System             | 2x System FAN                                      |

| Operating System           | Win XP/ Linux/Windows 2008                         |

| Environmental & Mechanical |                                                    |

| Operating Temperature      | 0°C~60°C                                           |

| Storage Temperature        | -40℃~85℃                                           |

| Relative Humidity          | 95%                                                |

| Vibration Test             | GB/T9813-2000                                      |

| EMC                        | Class B                                            |

| Dimension                  | 436mm×467.5mm×88mm (W×D×H)                         |

| Surface Treatment          | Paint Coating                                      |

| Installation               | 2U rack-mountable                                  |

| Color                      | Black                                              |

# MORICO

# Chapter 2 Installation Instruction

## **Chapter 2** Installation Instruction

#### 2.1 FW-7911 Structure View

#### 1. Full View

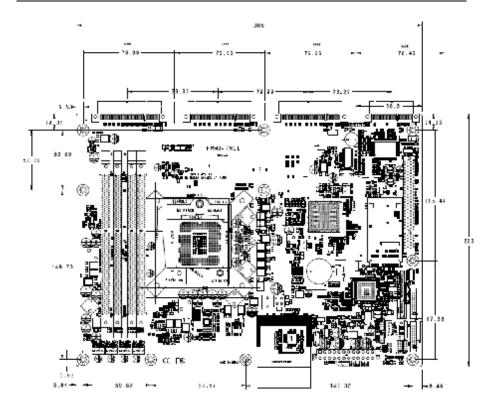

#### 2.2 Outline Dimension

Following Picture illustrates the dimension of network motherboard FWMB-7911 V1.1. Please follow the diagram and read the manual carefully to install the device. Otherwise, improper installation of some components will lead to system failure.

Note: When handling the device, please wear the antistatic gploves so as to avoid damage to some components.

#### 2.3 Install CPU and UDDIMM

Key components of this motherboard are Integrated circuit which will be easily damaged by electrostatic influence. So, before installing this board, please mind the precautions below:

- 1. Hold the board by the edges; don't touch any components or pins on the board

- 2. Use a grounded antistatic wrist strap/gloves while touching the integrated circuit component s (such as CPU, RAM).

- 3. When the integrated circuit components are uninstalled, pls put these components in antistatic tray or bags.

- 4.Pls make sure the power is disconnected before inserting the power plug.

#### 2.3.1 Install CPU

Please follow the steps below to install CPU:

- (1) Open the cover of the motherboard CPU socket

- (2) Hold two sides of the CPU and the triangle of its PIN1 will fit the socket alignment key into the CPU notch, then press the CPU into CPU socket.

- (3) Check the installation and close the cover of the CPU socket. Pls do not force the CPU into the socket which will bend the connectors on the socket and damaging the CPU Please follow the steps below to install CPU FAN:

- (1) Make sure the heat sink of the CPU in good connection with the CPU surface, then fix the fan on the motherboard.

- (2) Connect the FAN Power cord to the CPUFAN1 socket on the board

#### 2.3.2 Install UDDIMM

Board provides 4x UDDIMM slots. When installing the UDDIMM, pls mind following two points:

- When installing, please align the UDDIMM notch with the socket notch and then insert

the UDDIMM into the socket

- 2. Please choose the memory bank which can match your motherboard.

### 2.4 Jumper Setting

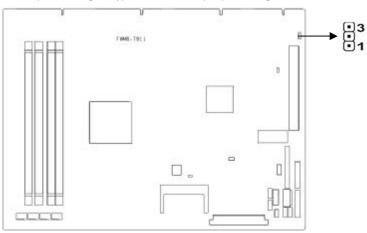

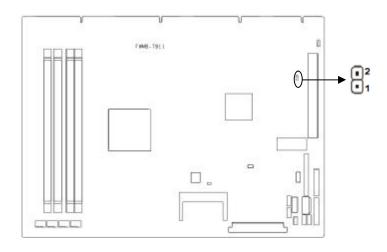

#### 2.4.1 CMOS Clearance/Hold Jumper Setting (JCC)

CMOS is powered by onboard button battery. Clean CMOS will lead to a permanent elimination of the previous system setting and back to the original (default setting) system settings.

Steps: (1) Turn off the computer, disconnect the power supply

- (2) Use jumper cap short JCC Pin 1 and Pin 2 for 5~6 sec, Then restore the default setting of Pin2 and Pin 3.;

- (3) Turn on the computer, then press DEL key into the BIOS setting, you can also reload optimal defaults.

- (4) Save and exit the setting interface

| Setting | JCC                                              |

|---------|--------------------------------------------------|

| 1-2     | Clear CMOS content, BIOS back to initial setting |

| 2-3     | Nomal status(default)                            |

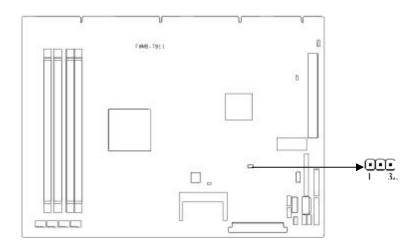

#### 2.4.2 WDOG Setup

To setup Watchdog or Bypass function via jumper setting

| Setting | WDOG     |

|---------|----------|

| 1-2     | WATCHDOG |

| 2-3     | Bypass   |

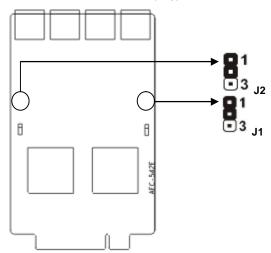

#### 2.4.3 AFC-542E V1.2 Pins (J1, J2)

J1 and J2 are used to setup Bypass function.

#### J1:

| Setting | Bypass                                                     |

|---------|------------------------------------------------------------|

| 1-2     | Power off-bypass, Power on- no bypass                      |

| 2-3     | Power off -bypass, Power on- bypass under software control |

#### J2:

| Setting | Bypass                                                    |

|---------|-----------------------------------------------------------|

| 1-2     | Power off-bypass, Power on- no bypass                     |

| 2-3     | Power off-bypass, Power on- bypass under software control |

### 2.5 Interface Description

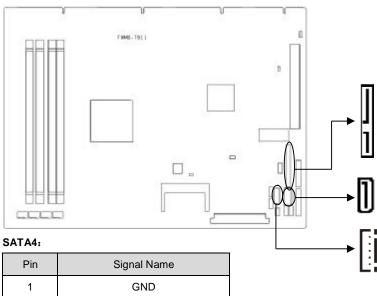

#### 2.5.1 SATA and SATA Power Interface

Board provides 2x SATAII (one 7+15Pin connector and one 7PIN connector.RAID 0/1 supported.

| Pin | Signal Name |

|-----|-------------|

| 1   | GND         |

| 2   | SATA_TXP    |

| 3   | SATA_TXN    |

| 4   | GND         |

| 5   | SATA_RXN    |

| 6   | SATA_RXP    |

| 7   | GND         |

#### SATA1:

| Pin      | Signal Name |

|----------|-------------|

| 1        | GND         |

| 2        | SATA_TXP    |

| 3        | SATA_TXN    |

| 4        | GND         |

| 5        | SATA_RXN    |

| 6        | SATA_RXP    |

| 7        | GND         |

| 8、9、10   | VCC3        |

| 11、12、13 | GND         |

| 14、15、16 | VCC  |

|----------|------|

| 17、18、19 | GND  |

| 20、21、22 | +12V |

#### SATA Power Interface S\_PWR1:

| Pin | Signal Name |

|-----|-------------|

| 1   | +12V        |

| 2   | GND         |

| 3   | VCC         |

| 4   | GND         |

| 5   | VCC3        |

#### 2.5.2 CF Card Socket (Compact Flash)

Rear Panel provides one 50Pin standard CF Card Socket, supporting Type I / II CF card.

#### 2.5.3 USB (USB23, USB45, 2x standard USB)

Board provides 2 set 2x5Header USB2.0 (USB23, USB45) and one standard double-deck USB port. 2x5Pin USB signal of USB23,USB45 can be connected to standard USB socket with a convert cable, up to 4x standard USB sockets.

#### USB23, USB45:

| Signal Name | Pin |    | Signal Name |

|-------------|-----|----|-------------|

| +5V         | 1   | 2  | GND         |

| USB DATA-   | 3   | 4  | GND         |

| USB DATA+   | 5   | 6  | USB DATA+   |

| GND         | 7   | 8  | USB DATA-   |

| GND         | 9   | 10 | +5V         |

#### Standard USB:

| Pin | Signal Name |  |  |

|-----|-------------|--|--|

| 1   | +5V         |  |  |

| 2   | USB DATA-   |  |  |

| 3   | USB DATA+   |  |  |

| 4   | GND         |  |  |

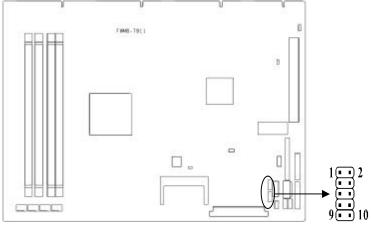

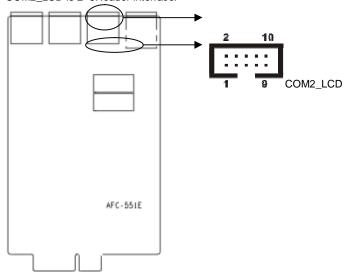

#### 2.5.4 Serial Ports

AFC-551E V1.0 card provides 2x serial ports, among which COM1-RJ is RJ45 and COM2 LCD is 2×5Header interface.

#### COM1-RJ:

| Pin | Signal Name |  |  |  |

|-----|-------------|--|--|--|

| 1   | HRTS#1      |  |  |  |

| 2   | HDTR#1      |  |  |  |

| 3   | HSOUT1      |  |  |  |

| 4   | NC          |  |  |  |

| 5   | GND         |  |  |  |

| 6   | HSIN1       |  |  |  |

| 7   | HDSR#1      |  |  |  |

| 8   | HCTS#1      |  |  |  |

#### COM2\_LCD:

| Signal Name | Pin |    | Signal Name |

|-------------|-----|----|-------------|

| HDCD#       | 1   | 2  | HDSR#       |

| HSIN        | 3   | 4  | HRTS#       |

| HSOUT       | 5   | 6  | HCTS#       |

| HDTR#       | 7   | 8  | HDI#        |

| GND         | 9   | 10 | 5V_LCD      |

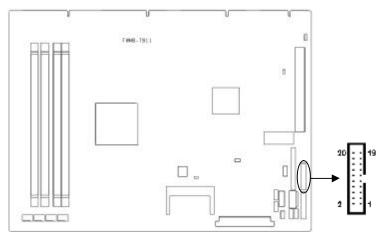

#### 2.5.5 Parallel Port (LPT)

Board provides one 2×10Pin parallel port, capable of connecting external parallel devices based on needs.

LPT:

| Signal Name | Pin |    | Signal Name |

|-------------|-----|----|-------------|

| T_STB#      | 1   | 2  | T_AFD#      |

| PDQ0        | 3   | 4  | T_ERR#      |

| PDQ1        | 5   | 6  | T_INIT#     |

| PDQ2        | 7   | 8  | T_SLIN#     |

| PDQ3        | 9   | 10 | GND         |

| PDQ4        | 11  | 12 | GND         |

| PDQ5        | 13  | 14 | GND         |

| PDQ6        | 15  | 16 | T_BUSY      |

| PDQ7        | 17  | 18 | T_PE        |

| T_ACK#      | 19  | 20 | T_SLCT      |

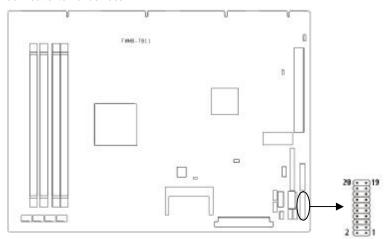

#### 2.5.6 LPC (JLPC)

Board provides one 2×10Pin LPC (Low Pin Count Interface Specification) interface to connect external devices.

JLPC:

| S          | Pin |   | Signal Name |

|------------|-----|---|-------------|

| LPC_PCLK   | 1 2 |   | GND         |

| LPC_FRAME# | 3   | 4 | NC          |

| PLTRST#    | 5   | 6 | VCC         |

| LPC_AD3      | 7  | 8  | LPC_AD2      |

|--------------|----|----|--------------|

| VCC3         | 9  | 10 | LPC_AD1      |

| LPC_AD0      | 11 | 12 | GND          |

| SMB_MAIN_CLK | 13 | 14 | SMB_MAN_DATA |

| V3.3SB       | 15 | 16 | SER_IRQ      |

| GND          | 17 | 18 | NC           |

| SUS_STAT#    | 19 | 20 | LPC_LDRQ#    |

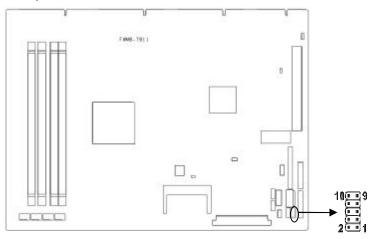

#### 2.5.7 GPIO (JGP)

Board provides one 2×5Pin GPIO Interface.

#### JGP:

| Signal Name | Pin |    | Signal Name |

|-------------|-----|----|-------------|

| PCH_GPIO72  | 1   | 2  | VCC         |

| PCH_GPIO28  | 3   | 4  | PCH_GPIO0   |

| PCH_GPIO31  | 5   | 6  | PCH_GPIO8   |

| PCH_GPIO32  | 7   | 8  | PCH_GPIO29  |

| GND         | 9   | 10 | PCH_GPIO15  |

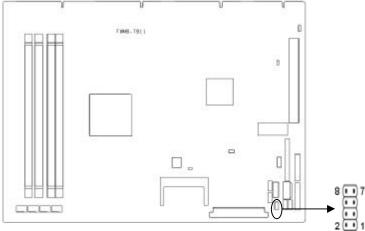

#### 2.5.8 Keyboard and Mouse Connector (KM)

Board provides one 2×4Header keyboard and mouse connector, to connect keyboard and mouse with a convert cable.

#### KM:

| Signal Name | Pin |   | Signal Name |

|-------------|-----|---|-------------|

| VCC         | 1   | 2 | MS_CLK      |

| GND         | 3   | 4 | MS_DATA     |

| KB_DATA     | 5   | 6 | GND         |

| KB_CLK      | 7   | 8 | VCC         |

#### 2.5.9 MINI\_PCIE (MINI\_PCIE, J\_LLED)

Board provides one standard MINI\_PCIE port. Users can expand their MINI\_PCIE devices based on actual needs. If using the MINI\_PCIE wireless LAN Card, the LED indicator will show the network status.

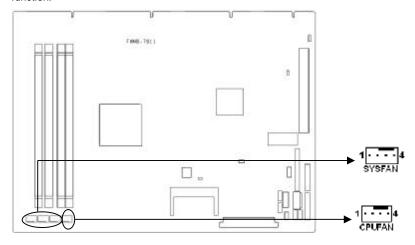

#### 2.5.10 FAN Connector (CPUFAN1, SYSFAN1-3)

Board provides one 4Pin CPUFAN and three 4Pin SYSFAN connector.

Please bear the following two points in mind when using the FAN Connector:

- (1)Fan power current should not above 350 mA (4.2W, 12V)

- (2)Please make sure the fan cable can match the socket wiring. Power line (generally red) in the middle. Ground wire (generally black) and FAN speed output pulse signal line (other color). Some fans without speed detection function will cause damage to the motherboard if the power output above 12V. Recommend to use the fan with speed detection function.

FAN:

| Pin | Signal Name |  |  |

|-----|-------------|--|--|

| 1   | GND         |  |  |

| 2   | +12V        |  |  |

| 3   | FANIN       |  |  |

| 4   | FANOUT      |  |  |

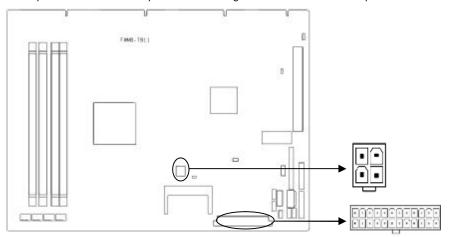

#### 2.5.11 Power Interface (ATX, PWR)

Board provides standard ATX power interface together with one 4Pin12VP4 power interface.

ATX:

| Signal Name | Pin |    | Signal Name |

|-------------|-----|----|-------------|

| +3.3V       | 1   | 2  | +3.3V       |

| GND         | 3   | 4  | +5V         |

| GND         | 5   | 6  | +5V         |

| GND         | 7   | 8  | PWR OK      |

| +5VSB       | 9   | 10 | +12V        |

| +12V        | 11  | 12 | +3.3V       |

| +3.3V       | 13  | 14 | -12V        |

| GND         | 15  | 16 | PS-ON#      |

| GND         | 17  | 18 | GND         |

| GND         | 19  | 20 | NC          |

| +5V | 21 | 22 | +5V |

|-----|----|----|-----|

| +5V | 23 | 24 | GND |

#### PWR:

| · | 1 | GND | 2 | GND | 3 | +12V | 4 | +12V |

|---|---|-----|---|-----|---|------|---|------|

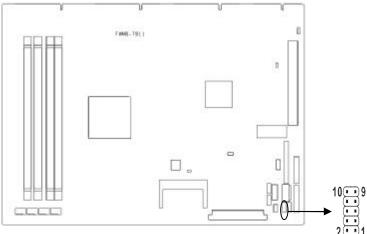

#### 2.5.12 Front Panel Connector (JFP)

JFP is used to connect the functional buttons and LED indicators on the front panel.

JFP:

| Signal Name  | Р | in | Signal Name |  |

|--------------|---|----|-------------|--|

| POWER LED+   | 1 | 2  | POWER LED-  |  |

| HD LED+      | 3 | 4  | HD LED-     |  |

| NC           | 5 | 6  | GND         |  |

| RESET BUTTON | 7 | 8  | GND         |  |

| POWER BUTTON | 9 | 10 | GND         |  |

#### 2.5.13 PCI Expansion Slot

Board provides one 120pin standard PCI expansion slot.

#### 2.5.14 PCIE Expansion Slot

Adopt standard PCIE×8 expansion slot. CPU has PCIEX4×4, adopting PCIEX8×2 expansion slot. The module adopts INTEL82576EB×2.Each expansion slot provides 4 electrical interface and 4x Optical port. PCH has PCIE X4, provided to INTEL82574L ×2, MINI PCIE and SM750 graphics.

#### 2.6 Network Module Description

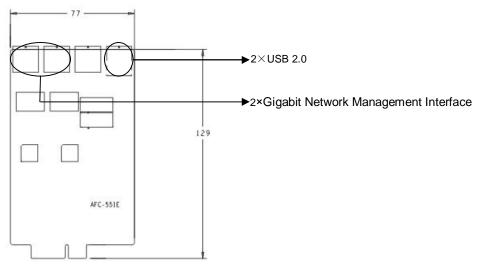

#### 2.6.1 AFC-551E

Adopt 2x Intel 82574L to expand 2x Gigabit Network Management Interface, 2x USB2.0 AND 1x RJ 45 serial port.

| LILED (Green) | Function                  | ACTLED (Yellow) | Function             |

|---------------|---------------------------|-----------------|----------------------|

| On            | 100/1000M<br>connectivity | Flash           | Data<br>transferring |

| Off           | 10M connectivity or Close | Off             | No data/Stop         |

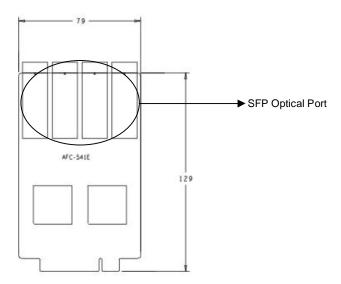

#### 2.6.2 AFC-541E

Adopt 2x Intel 82576EB to expand 4x Gigabit Network Interface (SFP optical port) , to connect with motherboard via PCIE $\times$ 8 connector.

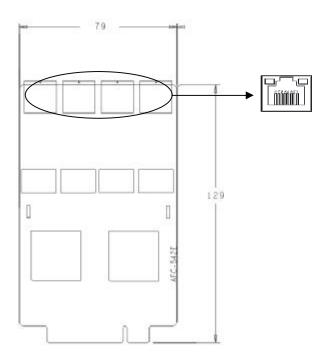

#### 2.6.3 AFC-542E

Adopt 2x Intel 82576EB to expand 4x Gigabit Network Interface (RJ45 electrical interface) It hase 2 set BYPASS function and is connected with motherboard via PCIE×8 connector. Users can config the BYPASS function via jumper setting, details pleased refer to Chapter 2-2.4.3 "AFC-542E V1.2 Pins".

| LILED (Green) | Function                  | ACTLED (Yellow) | Function             |

|---------------|---------------------------|-----------------|----------------------|

| On            | 100/1000M<br>Connectivity | Flash           | Data<br>Transferring |

| Off           | 10M Connectivity or Close | Off             | No data/Stop         |

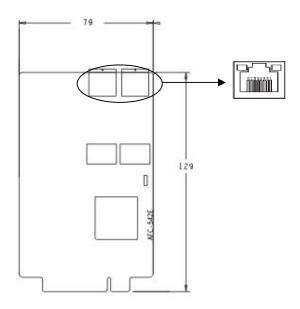

#### 2.6.4 AFC-542E-2x RJ45 LAN Port

Adopt 1x Intel 82576EB to expand 2x Gigabit Network Interface (RJ45 electrical interface). It has one group BYPASS function. Users can config the BYPASS function via jumper setting, details pleased refer to Chapter 2- 2.4.3 "AFC-542E V1.2 Pins".

| LILED (GREEN) | Function                  | ACTLED (Yellow) | Function             |

|---------------|---------------------------|-----------------|----------------------|

| On            | 100/1000M<br>connectivity | Flash           | Data<br>transferring |

| Off           | 10M connectivity or close | Off             | No data/Stop         |

# Chapter 3 BIOS Setup

#### **AMI BIOS Upgrading**

BIOS functions as a bridge connecting hardware and operating system. Hardware and software are upgrading all the time, so when your system goes wrong, for example, your system can not support the newest CPU, you need to upgrade BIOS to keep up with the latest technology.

AFUDOS.EXE is the FLASH IC program for BIOS to upgrade, which needs to be run in DOS mode.

Pls use a boot disk to load DOS, then run AFUDOS.EXE to upgrade BIOS ( for example: write XXXX.ROM into FLASH IC )

#### Oder format:

A:\ Afudos XXXX.rom

If you need to add other parameters, pls add <space>/? after the order format

Example: Afudos 7911I100.rom /P /B /C /N /X

#### Remarks:

- 1. BIOS upgrading is only executed when your system goes wrong.

- 2. Please use the upgrading program in the driver disk provided by us or download the latest version from related websites.

- 3. Please do not power off or reboot the system when upgrading, otherwise, the BIOS may be damaged or system may not be able to boot again.

- 4. Please backup your BIOS before upgrading

#### **AMI BIOS Description**

When the computer is power on, BIOS will conduct self-diagnosis to its hardware on motherboard and configure hardware parameter, finally the operating system will take control. BIOS is the communication bridge between hardware and O/S. Correct configuration of BIOS is critical for maintaining system stability and its optimized performance.

#### **BIOS Parameter Configuration**

Power on your computer, when this information display in your screen: Del->SETUP please press "DEL", then it will enter BIOS setup interface.

- 1. Power on or Reset computer.

- 2. When "Press <Del> to enter setup" in screen, please press <Del>.

- 3. Use the "←↑→↓"to choose the option which your want to modify, press <Enter> and enter into the sub-menu.

- 4. Use the " $\leftarrow \uparrow \rightarrow \downarrow$ " and <Enter> to modify the value.

- 5. At any time, press<Esc> can go back to the father-menu

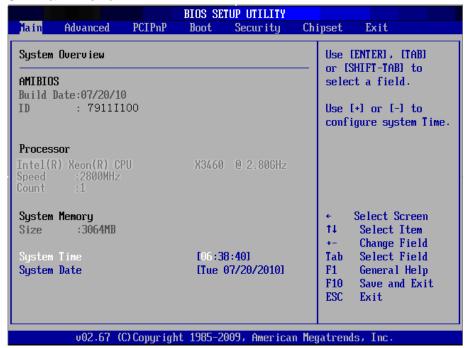

#### 3.1 Main Menu

#### AMI BIOS (Read Only)

BIOS information: such as BIOS version, Build date and BIOS ID

#### Processor (Read Only)

CPU information, such as the processor speed.

#### System Memory (Read Only)

This section shows the size of the system memory

#### **System Time**

System time format: Hour/Minute/Second

#### System Date

Setup system date. Format: Week/Month/Day/Year

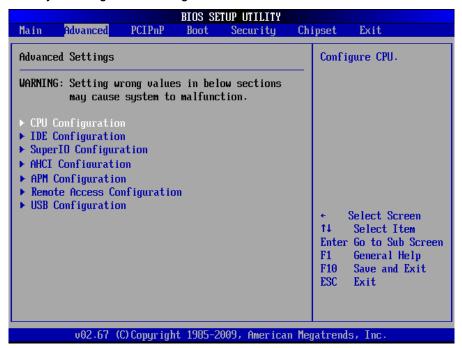

#### 3.2 Advanced Menu

Note: Incorrect parameter setup may lead to system failure, please setup this section carefully according to the following instructions.

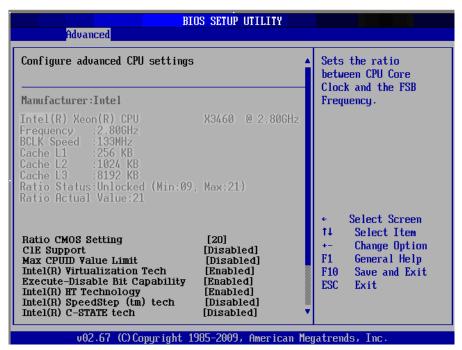

#### 3.2.1 CPU Configuration

The Read-Only option contains the detailed information of CPU, including CPU manufacturer, type, frequency, L1 cache and L2 Cache, etc.

#### Ratio COMS Setting

This option is used to setup CPU frequency doubling)

#### C1E Support

CPU C1E Support Option. Users can choose [Disabled] and [Enabled].

#### Max CPUID Value Limit

Please set this item as [Enabled] if the system OS doesn't support the extended CPUID function. Available options are [Disabled] and [Enabled].

#### Intel (R) Virtualization Tech

Intel virtualization technology enables to run multiple O/S of the same kind or different kind by using the same physical platform so as to realize the management and allocation of computer resources, maxmizing the resource utilization,

#### **Execute-Disable Bit Capability**

Execute Disable Bit (EDB) is a hardware-based security feature that introduced to its new generation CPU by Intel, which can help reduce system exposure to viruses and malicious code. EDB allows the processor to classify areas in memory where application code can or cannot execute. To use Execute Disable Bit you must have Windows XP SP2 operating system to support this function.

#### Intel (R) SpeedStep (tm) tech

This option is used to enable or disable Intel SpeedStep Technology

#### Intel (R) C-STATE tech

It is a technology by intel which allows the OS to independently lower the frequency of the cores when the need be thus saving power. If it's disabled then both the cores will run at a fixed frequency. Enabling it will allow the OS to make the core's run at different frequencies thus making optimum use of power. Set as [Disabled] when overclocking. If set as [Enabled], then the "C State Package Limit Setting" option will show.

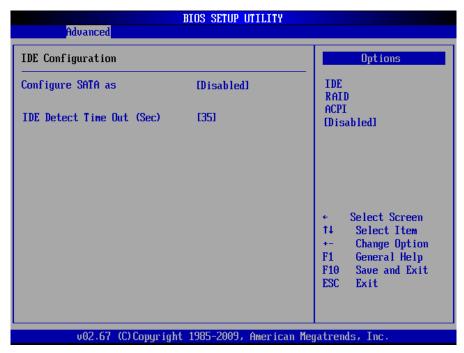

#### 3.2.2 IDE Configuration

#### Configure SATA as

SATA Configuration Mode Select. Available options are [RAID], [AHCI] and traditional [IDE].

#### IDE Detect Time Out (Sec)

Set BIOS searching IDE device in appointed time (by seconds)

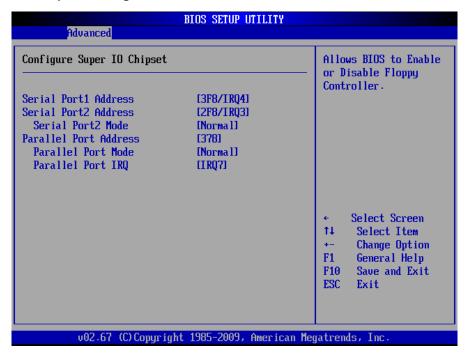

## 3.2.3 SuperIO Configuration

#### Serial Port1/2 Address

This option is used to config the interrupt and address of serial port1/2. Default set is recommended.

## **Serial Port2 Mode**

This option is used to config the mode of serial port2. Default set is [Normal]

#### Parallel Port Address

This option is used to config parallel port address, the defaut value is 378. Available cofig value including 378\278\3BC\Disabled

### **Parallel Port Mode**

This option is used to config the parallel port mode. Defaut set is [Normal]

#### Parallel Port IRQ

This option is used to config parallel port interrupt. Defaut value is IRQ7

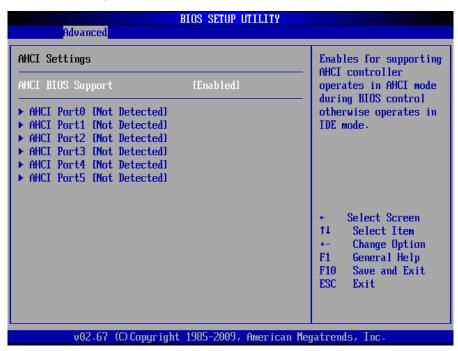

## 3.2.4 AHCI Configuration

#### **AHCI BIOS Support**

[Enabled] for supporting AHCI controller operates in AHCI mode during BIOS control otherwise operates in IDE mode.

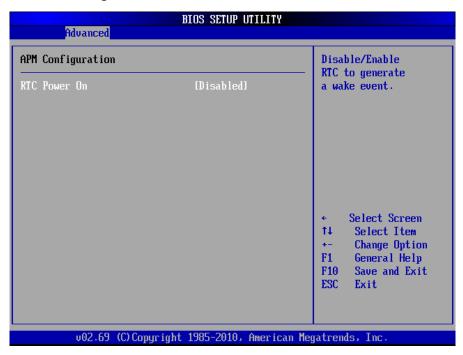

## 3.2.5 APM Configuration

#### RTC Power On

When Enabled, users can set the date and time at which the RTC (real time clock) alarm awakens the system from Suspend mode. The choices :< Enabled>, <Disabled>.

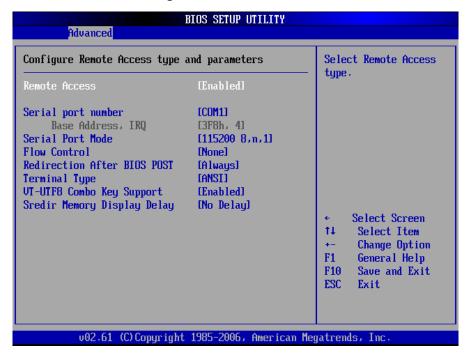

## 3.2.6 Remote Access Configuration

#### **Remote Access**

[Enabled] and [Disabled] options are used to open or close the remote accesse to BIOS.

## Serial Port number

Select Serial Port Number. Available options include [COM1] and [COM2].

#### **Serial Port Mode**

This option is used to select serial port transmission rate.

#### Flow Control

Network Flow Control. Available options include [None][Hardware][Software].

#### **Redirection After BIOS POST**

# **Network Security Barebone**

Whether to activate the redirection function after BIOS Post. Available options include Disabled] [BootLoader] and [Always].

## **Terminal Type**

Select the terminal type. Options include [ANSI] and [VT100].

## **VT-UTF8 Combo Key Support**

[Enabled] option will enable the system the VT-UTF8 Combo Key Support. [Disable] will disable the support.

## **Sredir Memory Display Delay**

Sredir Memory Display Delay Selection. Options include [NO Delay],[ Delay 1Sec] ,[Delay 2Sec] and [Delay 4Sec].

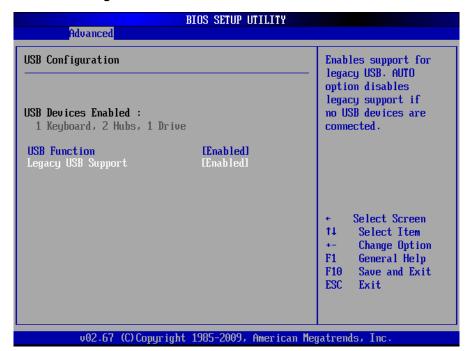

## 3.2.7 USB Configuration

## **USB Devices Enabled (Read Only)**

This option will show the USB devices that are connected with Motherboard.

#### **USB Function**

This option is used to open or close the USB port on the motherboard, default as Enabled.

## **Legacy USB Support**

If need support USB device in DOS mode: such as USB Flash Disk, USB keyboard, then select <Enabled> or<Auto>. If not , pls select < Disabled>

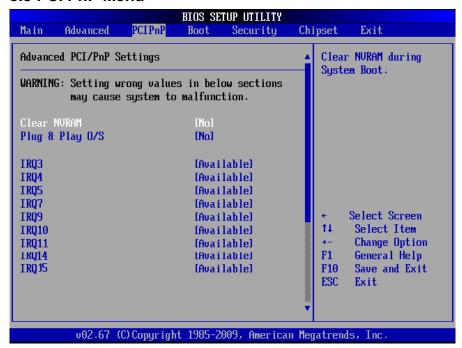

## 3.3 PCI PnP Menu

## **Clear NVRAM**

Select to clear NVRAM data or not.

[NO] for keeping the data

[YES] for clearing the data

## Plug & Play O/S

This option is for selecting BIOS or PnP O/S to allocate the interrupted resource in the peripheral devices.

Choose [YES], O/S will automatically allocate the resources If O/S doesn't have the PnP function, pls set this option as [NO].

#### **IRQ3-15**

This is used to keep the IRQ interrupt or allocate the interrup to PCI devices.

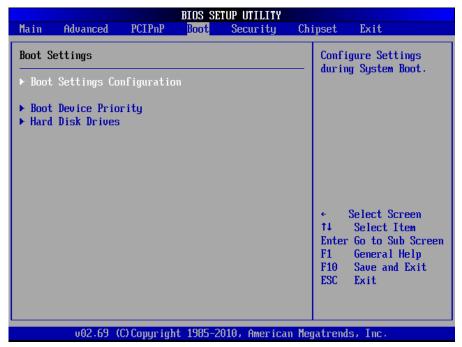

# 3.4 Boot Menu

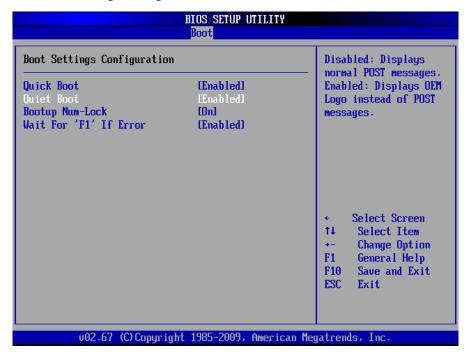

## 3.4.1 Boot Settings Configuration

#### **Quick Boot**

<Enabled>: BIOS will skip self-detection and accelerate POST

<Disabled>: After BIOS detect load Windows O/S.

## **Quiet Boot**

This option will show the spplier's Logo on the screen picture when booting the computer.

<Disabled> for close and <Enabled> for open.

#### **Boot Up Num-Lock**

This option is used to activate the Num-lock after booting the DOS system. <ON> for uncloking the number key and <OFF> for locking the number key.

#### Wait For "F1" If Error

If error occurs, wait for "F1". When the error doesn't lead to power down, then following messages will show: "Press 'F1' to resume" or "Press' F1' to Setup", users can press F1 to make the system go on working.

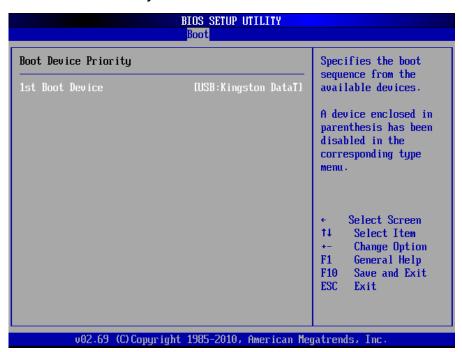

## 3.4.2 Boot Device Priority

This is used to setup the boot device priority.

Press "Enter" then the following sub-menu will show:

#### 1st Boot Device

System will detect devices by this priority until it finds an available boot device.

(Boot device can be the Removable Drive or the Hard Disk Drive)

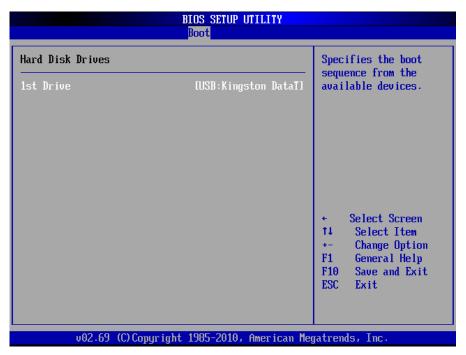

## 3.4.3 Hard Disk Drives

#### Boot device set for HDD

If multi- HDD be connected, user must set up their priority. The HDD of the highest priority will display in "Boot Device Priority"

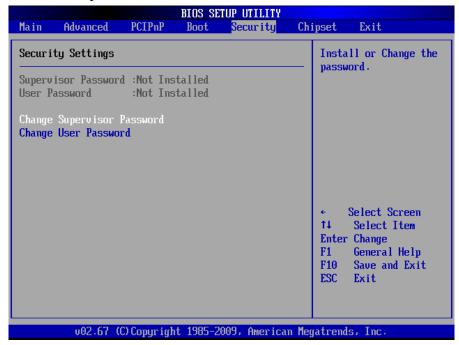

# 3.5 Security Menu

## **Supervisor Password**

If you set up the password, it will display "Installed"

If not, it will display "Not Installed"

#### **User Password**

If you set up the password, it will display "Installed"

If not, it will display "Not Installed"

## **Change Supervisor Password**

Press 'Enter' under this option, then enter sub-menu to change the password.

## **Change User Password**

Press 'Enter' under this option, then enter sub-menu to change the password.

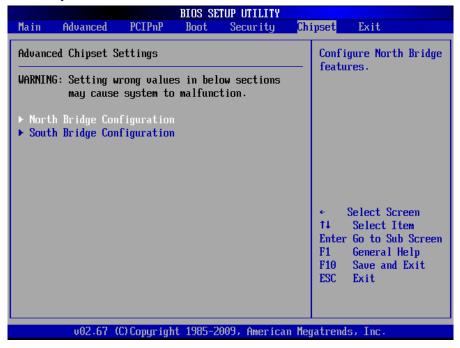

# 3.6 Chipset Menu

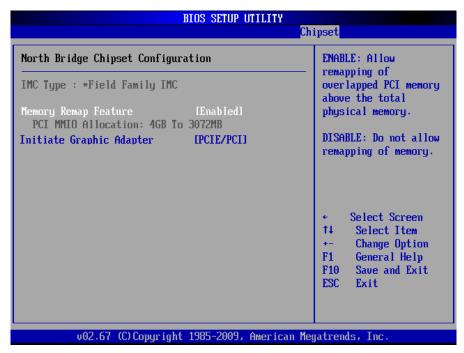

## 3.6.1 North Bridge Configuration

## **Memory Remap Feature**

[Enabled]: Allow remapping of overlapped PCI memory above the total physical memory

## **Initate Graphic Adapter**

Initiate Graphic Adapter Selection

[Disabled]: Do not allow remapping of memory

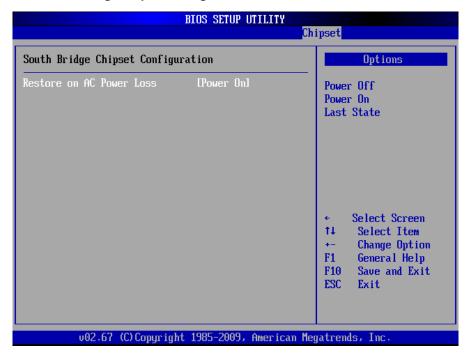

## 3.6.2 South Bridge Chipset Configuration

#### **Restore on AC Power Loss**

This option is for setting the system status while connecting the power again after the AC

Power Loss

<Power Off>:System remains the status of power off

<Power On>: System will reboot automatically

<Last State>: Remain the same as the status before the power loss

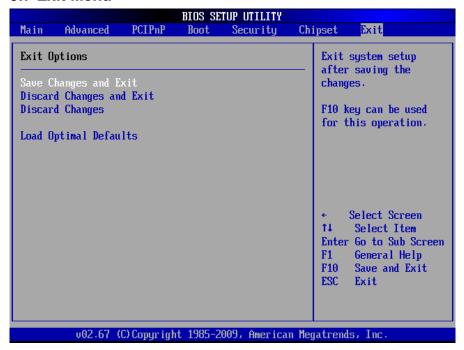

## 3.7 Exit Menu

#### Save Changes and Exit

Press <Enter> and <Enter> under this option, to save BIOS changes and reboot system.

## **Discard Changes and Exit**

Press <Enter> and <Enter> under this option, to discard BIOS changes and exit the current interface.

#### **Discard Changes**

Press <Enter> and <Enter> under this option, then continue to setup BIOS

## **Load Optimal Defaults**

Recommend users first to select this option before BIOS Setup.

# **Appendix**

# Appendix 1; Watchdog Programming Guide

| watchdog Reference Code (ASM)                                                           |                                               |

|-----------------------------------------------------------------------------------------|-----------------------------------------------|

| Set the port to realize watchdog function through DEBUG order, so that it can carry out |                                               |

| Watchdog Timer's various functions.                                                     |                                               |

| port instruction:                                                                       |                                               |

| 2EH : Address register                                                                  |                                               |

| 2FH: Data register                                                                      |                                               |

| Example: Set Watchdog Timer for 30 Seconds, DEBUG in DOS:                               |                                               |

| C:\>debug                                                                               |                                               |

| -o 2e 87                                                                                |                                               |

| -o 2e 87                                                                                | ;Unlock                                       |

| -o 2e 2d                                                                                |                                               |

| -o 2f 20                                                                                | ;bit0=0 ,set pin as watchdog func             |

| -o 2e 07                                                                                |                                               |

| -o 2f 08                                                                                | ;Select Logic Devices                         |

| -o 2e 30                                                                                |                                               |

| -o 2f 01                                                                                | ;Activate Logic Devices                       |

| -o 2e f5                                                                                |                                               |

| -o 2f 00                                                                                | ;Set Timer Unit as Sec/ (set as min: o 2f 08) |

| -o 2e f6                                                                                |                                               |

| -o 2f 30                                                                                | ;Set Timer Count as 30h= 48 Second            |

| -o 2e aa                                                                                | ;Lock the register                            |

| -q                                                                                      |                                               |

| C:\>                                                                                    |                                               |

|                                                                                         |                                               |

| Upon the last line, Press "Enter", then system will reboot after counting 48 seconds    |                                               |

|                                                                                         |                                               |

| Reference Code (c++ language):                                                          |                                               |

# **Network Security Barebone**

outputb (0x2e, 0x87)

outputb (0x2e, 0x87)

outputb (0x2e, 0x2d)

outputb (0x2f, 0x20) //bit0=0 ,set pin as watchdog func

outputb (0x2E, 0x07)

outputb (0x2F, 0x08)

outputb (0x2F, 0x08)

outputb (0x2e, 0x30)

outputb (0x2f, 0x01) //active the device

outputb (0x2f, 0x00) // Set Timer Unit as Sec/ (Set as Min: outputb (0x2f, 0x08))

outputb (0x2f, 0x30) // Set Timer Count to 30h=48 sec.

outputb (0x2E, 0xAA)

//Lock SUPER IO Register

If system fails, watchdog can enable the system reboot automatically

# **Appendix 2: Glossary**

#### **ACPI**

Advanced Configuration and Power Management Interface for short. ACPI specifications allow OS to control most power of computer and its extended devices.

#### **BIOS**

Basic input/output system. It's a kind of software including all in/out control code interface in PC. It will do hardware testing while system booting, then system runs, it provides an interface between OS and hardware. BIOS is stored in a ROM chip.

#### **BUS**

In a computer system, it's the channels among different parts for exchanging data; it's also a group of hardware line. BUS here means part lines inside CPU and main components of memory.

#### Chipset

Integrated chips for executing one or more function. Here "Chipset" means system level chipset structured by Southbridge & Northbridge; it decides motherboard's structure and main functions.

#### **CMOS**

Complementary Metal-Oxide Semiconductor, a widely used semiconductor with the characteristic of high speed but low power. CMOS we mention here means part of obligate space in on-board CMOS RAM, for saving date, time, system information and system parameter etc.

#### COM

Computer-Output Microfilmer. A universal serial communication interface, usually adopts normative DB 9 connector.

#### DIMM

Dual Inline Memory Module. It's a small circuit board with memory chipset, providing 64bit bus width.

#### DRAM

Dynamic Random Access Memorizer. It's a normal type of memory often with a transistor and a capacitance to store 1 bit. With the development of the technology, more and more types and specification of ORAM exist in computer application. Now: SDRAM, DDR SDRAM and RDRAM are generally used.

#### I2C

Inter—Integrated Circuit, generically referred to as "two-wire interface", is a multi-master serial single-ended computer bus invented by Philips that is used to attach low-speed peripherals to a motherboard, embedded system, or cellphone

#### LAN

Network interface. Network grouped by correlative computers in a small area, generally in a company or a building. Local area network is buildup by sever, workstation, some communications links, as a rule. Terminals can access data and devices anywhere through cables, so, many users can share costly device and resource.

#### **LED**

Light-Emitting Diode. a semiconductor device that shines when power supply is connected, often use to denote info lightly, for example, to denote power on or HDD work normally. LPT: line print terminal. The denomination reserved by DOS, is used to denote universal parallel interface, and connect printer in a general way.

#### PnP

Plug-and-Play. It is a specification that allows PC to configure its external devices automatically and can work independently without the manual operation by its user . To achieve this function, its BIOS should be able to support PnP and a PnP expansion card

#### **POST**

Self-test when power on. While booting, BIOS will do once uninterrupted testing operation to the system, including RAM, keyboard, hard disk driver etc. Check them in normal situation and work well.

#### PS/2

A keyboard & mouse connective interface specification developed by IBM.PS/2 is a DIN interface with only 6PIN; it also can connect other devices, like modem.

#### USB

It is the Universal Serial Bus for short. A hardware interface adapts to low speed external devices, and is always used to connect keyboard, mouse etc. One PC can connect 127 USB devices Max, providing 12Mbit/s transmit bandwidth; USB supports hot swap and multi- data stream, namely, you can plug USB devices while system is running, system can auto-detect and makes it work on.

0

敬请参阅

http://www.norco.com.cn

本手册所提供信息可不经事先通知进行变更

华北工控对所述信息保留解释权